void C1\_reset(outC\_C1 \*outC) void C1(inC\_C1 \* inC, outC\_C1 \* outC)

#### 42-ization of existing code

**.**C

42 is not intended to be a new language to design embedded systems. The basic components may be implemented using any lan-The only restriction is to guage. be able to wrap the code in a 42component.

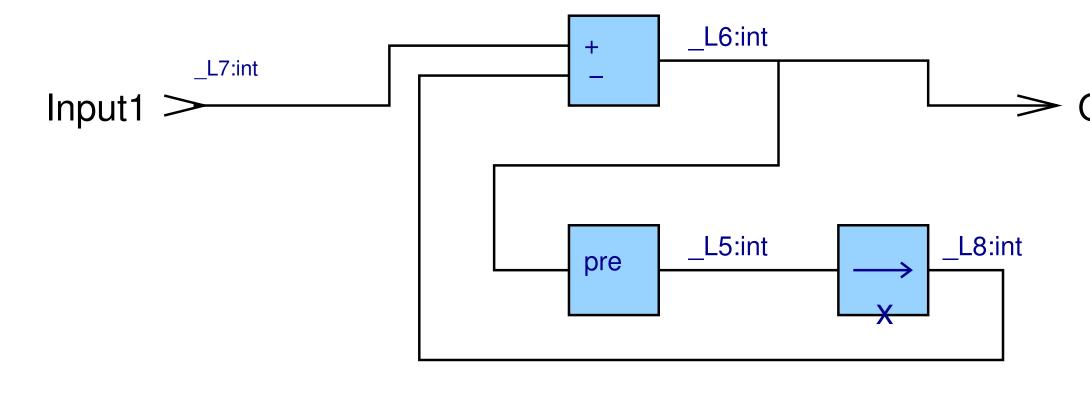

### Scade/Lustre diagram

# **Programmable Models of Computation for a Component–Based Approach** to Heterogeneous Embedded Systems

Florence Maraninchi, Tayeb Bouhadiba (Verimag/Grenoble INP) firstname.lastname@imag.fr

| 2 formalism                                                                                                                        |                                                   |

|------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

|                                                                                                                                    | 42 Overview                                       |

| me a component is activated                                                                                                        | 42 [1] is a component-based approach to the       |

| $_i$ , it consumes inputs, per-                                                                                                    | totyping of embedded systems. A component         |

|                                                                                                                                    | box with input and output data and control po     |

| an atomic computation, and                                                                                                         | ponents can be programmed in all languages        |

| es outputs.                                                                                                                        | they provide such an interface.                   |

|                                                                                                                                    |                                                   |

| locut                                                                                                                              | 42 focuses on the "System-Level view", i.e, the   |

| ic1 ic2 Input<br>Control Ports                                                                                                     | blage of components and the associated verifi     |

| terminating<br>atomic<br>step<br>internal memory<br>Output                                                                         | Protocol specificati                              |

| oc1 oc2 Output                                                                                                                     | 42 protocols                                      |

| Control Ports                                                                                                                      | The possible uses of a component are spec         |

|                                                                                                                                    | control-contract, called a "protocol". It may exp |

| c(outC_C1 *outC)                                                                                                                   | <ul> <li>Control sequencing</li> </ul>            |

| C1 *inC, outC_C1 *outC)                                                                                                            | * Data dependencies                               |

|                                                                                                                                    | <ul> <li>Control information</li> </ul>           |

| C code generation                                                                                                                  | <ul> <li>Conditional data dependencies</li> </ul> |

|                                                                                                                                    |                                                   |

| new                                                                                                                                |                                                   |

| SYS-                                                                                                                               | (id1 and id2) op / $\alpha$ :=ctl (od1)           |

|                                                                                                                                    |                                                   |

| may<br>lan-                                                                                                                        | $\rightarrow (0)$ $(1)$                           |

|                                                                                                                                    |                                                   |

| s to                                                                                                                               | (id1 and IF $\alpha$ THEN id2) op2 (IF            |

| 42-                                                                                                                                |                                                   |

| Lustre diagram                                                                                                                     | Using 42 Protocols                                |

|                                                                                                                                    | 42 protocols are used to verify assembla          |

| _L6:int                                                                                                                            | components and the compliance of the cor          |

| Output1                                                                                                                            | code w.r.t the components' protocols. The         |

|                                                                                                                                    | cation may be done statically (a model- ch        |

| $\begin{array}{c c} \underline{-L5:int} & \underline{-L8:int} & 1 \\ \hline \end{array} & \hline \end{array} & \hline \end{array}$ | problem) or dynamically.                          |

|                                                                                                                                    |                                                   |

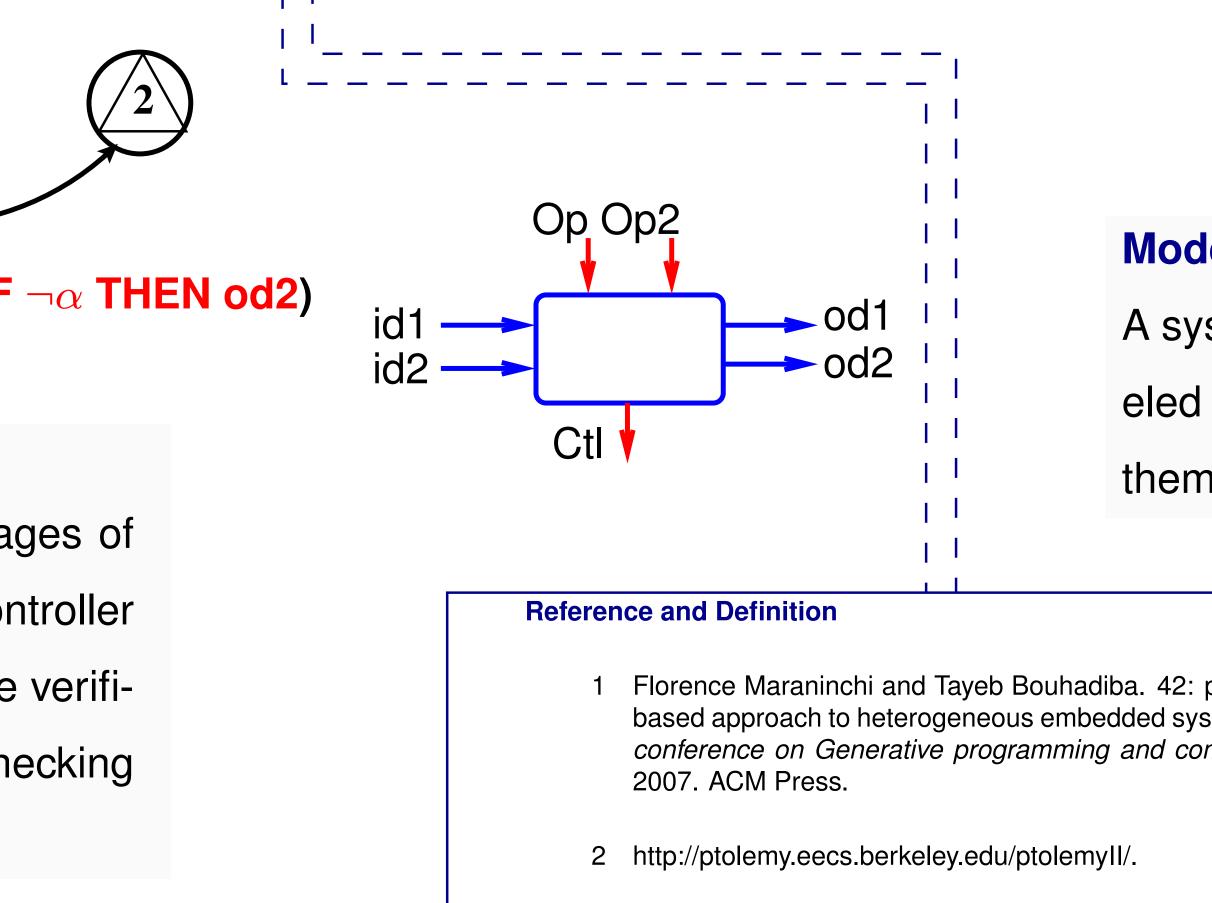

virtual prot is a black

orts. Com-

as long as

the assemications.

#### ion in 42

cified by a press:

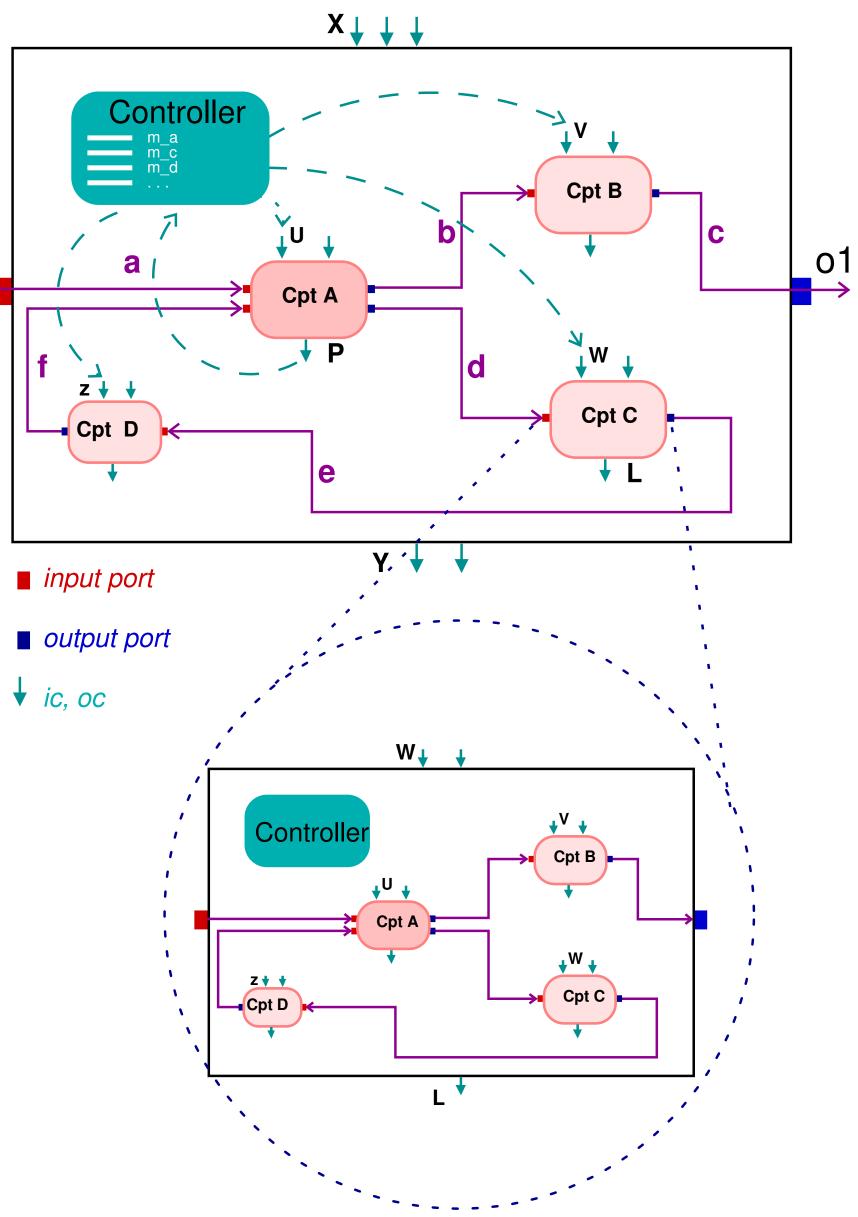

#### Controller is : var M : bool = true ; for X do :{ /\* defines X. m\_a, m\_b, m\_c: FIFO(1,int); m\_d, m\_e, m\_f: FIFO(4,int); if (M) { m\_a.put ; /\* reads i1. m\_a.get ; D.z;//\*activates D. m\_f.put ; m\_f.get ; A.u; m\_b.put; m\_d.put; $m_b.get; B.v; M = M or p;$ m\_c.put ; m\_c.get ;/\*assigns 01. m\_d.get ; C.w ; m\_e.put ; m\_e.get; D.k ; = ! M ; else { ... ] = M;/\*assigns Y.

A system

## The controller defines the MoCC [a]

The controller is a small program that could be implemented in any programming style. For each global activation (e.g., X) the controller is in charge of activating components, managing the memory associated with each wire. It assigns values to the global data and control output ports (e.g., Y, O1).

a MoCC : Model of Computation and Communication

### A system

A system is made of a set of components whose data ports are connected by oriented wires. The wires do not express any synchronization.

The semantics of the assemblage is defined by the controller (as in Ptolemy [2]).

#### Modeling heterogeneity

A system that needs several MoCCs is modeled with several levels of hierarchy, each of them having a specific controller.

Florence Maraninchi and Tayeb Bouhadiba. 42: programmable models of computation for a componentbased approach to heterogeneous embedded systems. In GPCE '07: Proceedings of the 6th international conference on Generative programming and component engineering, pages 53-62, Salzburg, Austria,